ESIstream IP – シリアル・インタフェースの設計を容易にします

まえがき

昨今の広帯域データコンバータを使用するうえでの大きな課題は、高速シリアル・インタフェースをどのように設計するかということです。ESIstreamは、設計への負担を最小限にするように考慮されたオープンソースのシリアルデータ・インターフェース・プロトコルであり、現存する様々なFPGAに非常に少ないリソースを使って、簡単に実装することができます。端的に言いますと、これはJEDECのJESD204Bサブクラス1と2標準のオープンソース版と言えます。しかし、この端的な説明では、ESIstreamユーザーにとってのいくつかの重要な利点が語られていません。その重要な利点というのは、大幅な簡易化がされていること、リンクレイテンシが低減されること、レイテンシを的確に把握できることです。以下に更に詳しく説明していきます。

本記事では、既に多くの文書がJESD204Bについて説明しているように、ESIstreamの構造にフォーカスして丁寧に説明しています。次に、ESIstreamとJESD204Bの違いを解説してから、皆様にESIstreamを御採用頂くために、ESIstreamのプロトコル開発を担ったTeledyne e2vが独自のESIstream VHDL IPを世に送ることを決定したというニュースを紹介します。

シリアル化の歴史

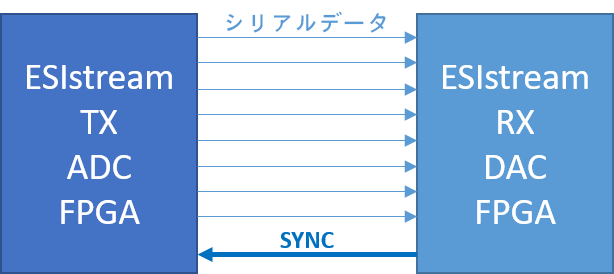

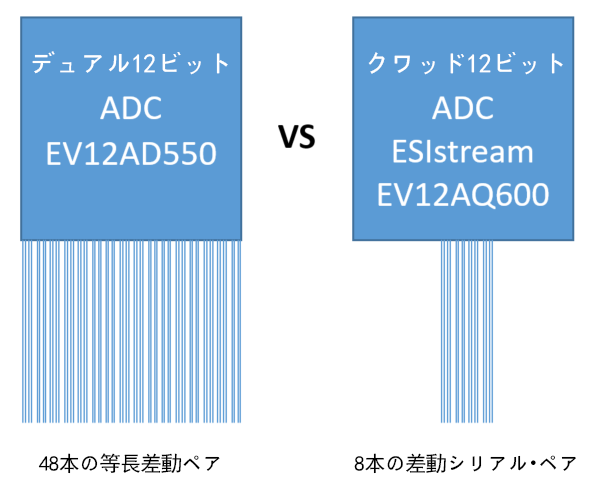

21世紀への変わり目を迎えたころ、CMOSプロセスと同じくデータコンバータ技術の進化も機能的な限界に達し始めていました。もともとサンプリング周波数が10MHz以上の高速ADC/DACはパラレルデータ・インターフェースを特徴としていましたが、これはプリント基板(PCB)に非常に多くの配線をしなければならなかったことを意味します(図1)。さらに、サンプルレートが増加した結果、出力データレートが高くなり、このことによってPCBの設計は著しく困難なものとなりました。データ・インターフェースのシリアル化(LVDS(低電圧差動信号)とシリアライザ/デシリアライザ(SERDES))は、クロックがデータストリームに埋め込まれるので、このデータ伝達課題への解決策となることが期待されました。PCBレイアウトの簡素化とフォームファクターの大幅な改善が期待されたのです。インターフェースの簡素化は、リンクの送信側、受信側両方の利点となります(図1)。シリアルリンクは、データレーンの配線長のマッチングへの制約を大幅に軽減でき、PCBの設計をさらに容易にしました。

図1 シリアルリンクがPCBの配線を容易に

しかし、広帯域データコンバータがもたらすシステムレベルの様々な課題を解決するシリアル・ソリューションが生まれるまでに、長い時間がかかりました。レイテンシを正確にコントロールすることは同時サンプリングの必要条件ですが、これを実現するまでには多大なる努力を必要としました。このことは、過去12年以上にわたるJESD204標準の変遷と、その代替となるオープンソース、ESIstreamを示した下表(表1)を見れば、一目瞭然です。

表1 シリアル・インタフェースの歴史

| LVDS | JESD204 | JESD204A | JESD204B サブクラス 1 | JESD204B サブクラス 2 | ESIstream | |

| リリース年 | 2001 | 2006 | 2008 | 2011 | 2011 | 2014 |

| レーンレート [Gbps] | 3.125 | 12.5 | 12.5 | 12.8 Gbps (EV12AQ600) トランシーバによってのみ制限される |

||

| マルチレーン同期 | いいえ | いいえ | はい | はい | はい | はい |

|

マルチデバイス同期 |

いいえ | はい | はい | はい | はい | はい(実証済) |

| 決定論的レイテンシ | いいえ | いいえ | いいえ | はい (fs > 500MSPS) |

はい (fs > 500MSPS) |

はい |

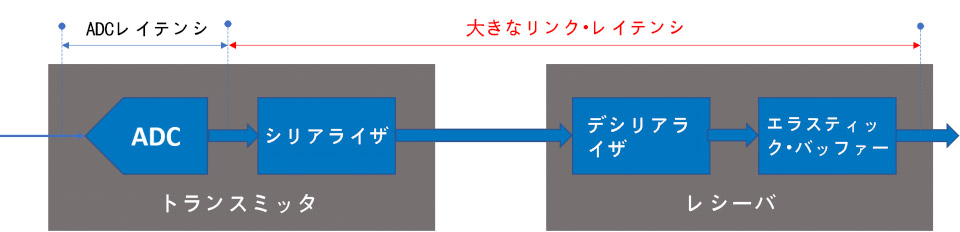

シリアル・インタフェースのより明白な利点のひとつは、分解能が高くなってもデバイスパッケージのデータラインを増やす必要がないということであり、このことによりピンカウントの制約が軽減されます。しかし一方で、欠点は伝送レイテンシが悪化するということであり、これはエンコード/デコード処理とパスエラスティック受信バッファリングによって生じます。

図2 シリアル化は追加のレイテンシを生み出す

シリアル化はまた、デバイスが必要とする出力ドライバの数を減らすことができるので、データコンバータの電力消費を減らすことができます。さらに、差動シリアルラインを使うことで、システムで発生する電気ノイズの影響を最小化して、必要なダイナミックレンジを確保することができます。また、符号化はスペクトル雑音を拡散させ、差動信号はクロストークの影響を最小化することに貢献します。

実際に、最近まで多チャンネルを同時にサンプリングする場合、初期のシリアルインターフェースではチャンネル間の同期を取ることが非常に困難で、開発者は非常に困難なボード設計してきました。

ESIstreamの仕様

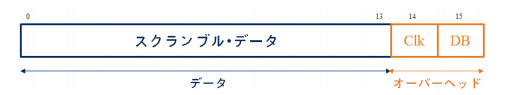

ESIstreamの基本を見てみましょう。ESIstreamは14b/16bデータ符号化アルゴリズムを使用し、最下位ビットから順次出力され、13 Gbpsを超えるレーンレートをサポートします。これは、12ビットや14ビット分解能のコンバータに適しています。プロトコルは線形フィードバック・シフトレジスタ・スクランブリング・プロセスを使用し、図3に示すようにディスパリティビットとクロック同期ビットを各データワードに追加します。(2ビットのオーバーヘッド)このことによって、符号化効率87.5%が得られますが、これはJESD204B(8b/10bit符号化ストリーム)より優れています。ディスパリティビット(DB)によってデータリンク間のDCバランスが確保され、CLKビットは切り替えることで同期モニタリングが可能になります。

図3 ESIstreamの基本データフレーム

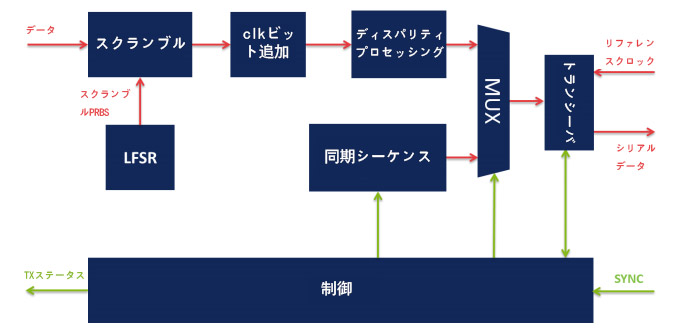

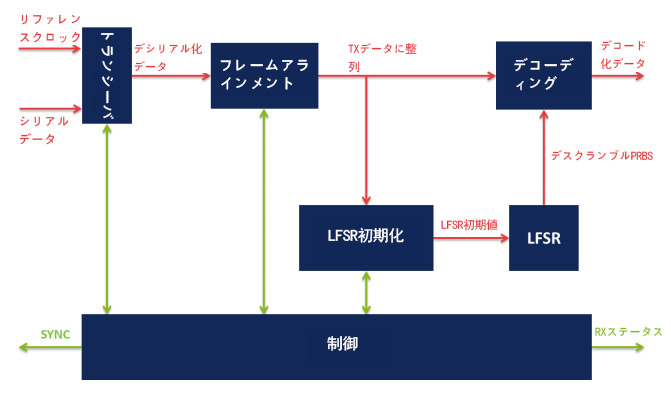

ESIstreamのトランスミッタ(Tx)とレシーバ(Rx)コアのハイレベル・ブロックダイアグラムを、以下の図4と図5に示します。

図4 ESIstreamのTxパス

図5 ESIstreamのRxパス

ESIstreamの符号化アルゴリズムは、シリアル・インターフェースの物理的な限界を緩和するために設計されました。もっとも重要なことは、トランスミッタとレシーバの間の配線がACカップルである必要があるということです。このことから、送信データの直流バランスが重要であり、問題があるとリンク・カップリングコンデンサーがドリフトを起こし、データ・アイが閉じて正しくデータを受信できなくなります。

レシーバ側では、クロック・データ・リカバリ(CDR)ブロックに通常PLLを用いて受信信号をクロックとデータに分離しますので、これにより送受信間でデータとは別にクロックラインを設ける必要がなくなります。しかし、CDRのPLLが安定的にロックして動作し続けることが必要になります。

送信データのスクランブリングは、統計的なDCバランスが考慮され、リンクがつながり続けることを保証するために実行されます。ESIstreamの開発者はデジタル設計の複雑性を可能な限り排除し、エラーの発生を最小限にするアルゴリズムを追求したのです。そのアルゴリズムは217-1長のフィボナッチ多項式に基づいていており、それに14ビットシフトを行っています。変換処理からで生成されるデータは、下の図6に示すように、リニアフィードバック・シフトレジスタデータ(疑似ランダムコード)との排他的論理和を取ります。

図6 LSFRコードとの排他的論理和によるスクラブルデータ生成

スクランブリング後に得られた14ビットのデータは、16ビットフレームにエンコードされます。2ビットのオーバーヘッドビットのうちの1ビットはクロックビットで、フレームごとにトグルします。もう1ビットはディスパリティビットで、ディスパリティ・カウンター(RDC)の状態に応じて設定されます。その結果、2種類のRDC状態が生じます。

- RDCが+/- 16未満のときはディスパリティ・ビットに0が設定されます。

- RDCが+/- 16以上のときはディスパリティ・ビットに1が設定され、データは反転されます。

これらの処理によって、受信側のPLLをロックさせるための要求が満たされ、リンク上のDCバランスの要求も満たされます。レシーバはまずディスパリティ・ビットを確認します。このビットが1に設定されている場合、受信データはデスクランブルの前に反転されます。ディスパリティ・ビットが0の場合はデータは直接デスクランブルされます。

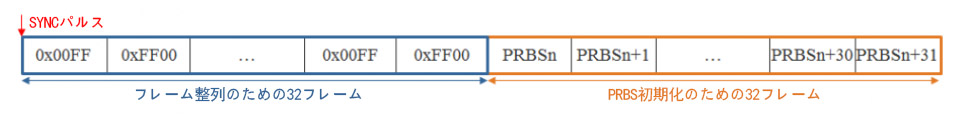

ESIstreamリンクを安定動作させるためには、まず第1にリンクが同期している必要があります。例えば、トランミッタとレシーバ両方のスクランブル・エンジンが同じ動作をして、データフレームをトランスミッタとレシーバ双方で正確に認識できることです。同期処理は2つの段階があります。すなわち、フレーム整列と、疑似ランダムビット・シーケンス(PRBS)初期化です。

図7 ESIstreamリンクの同期フレーム

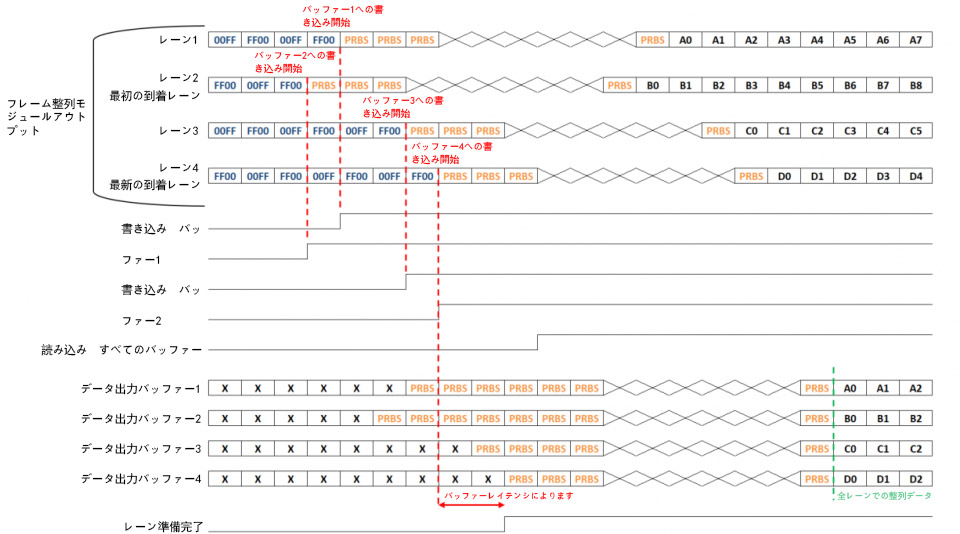

レシーバはSYNCパルスからプロセスを開始します。パルスは少なくとも1フレームの中で完了する必要があります。続いて、トランスミッタが32フレーム整列パターンを送ります(図5)。レシーバはフレーム整列パターンに対してはスクランブリングとディスパリティ・プロセスを行わず、トランスミッタに時間的に整合させます。整列フレームの直後にトランスミッタはさらに、14ビットのPRBSとクロック/ディスパリティ情報を含む32フレームのPRBSデータを送ります。正しく動作すると、レシーバのLFSRはPRBSワードで動作を開始します。この時点でリンクは同期されます(図8)。同期は、クロックビットを観測することでレシーバ内で継続監視することができます。クロックビットがフレーム毎にトグルしなかった場合、これは同期に問題があることを意味するので、リンクはリセットされて再同期されなければなりません。

図8 ESIstreamレシーバのレーン同期シーケンス

スクランブリング、クロックとディスパリティ・ビットの処理により、ESIstreamを使用したデータ送信が確実に実行されます。

ギガヘルツ・サンプリングシステムの同期 - 極端に心配する必要はありません

デジタル・ビームフォーミングを用いた無線システムは、信号を同時にサンプルするアンテナアレイが必要です。このアンテナアレイは、各アンテナノードの受信する信号の空間情報を維持します。このアプローチには複雑性と電力ロスといった問題がありますが、いくつかの価値のある利点があります。

- 高いS/N比(SNR)によってリンク数を増やすことが可能で、信号の帯域を広げることができます。

- アレイアンテナの空間特性を利用した干渉回避ができます。干渉は特定の方向から来るので、ビーム形成アルゴリズムにより干渉をキャンセルできます。

- 高いリンク効率が得られるので、レーダー・システムではより多くのターゲットを同時に追跡でき、また携帯電話ネットワークではより多くのユーザーが利用することができます。

今日では、多くのアプリケーションでビームフォーミング技術が使われており、ビーム形成技術では同時サンプリングが必要です。しかしGHzの周波数域においては、ICと基板レベルの双方での信号伝搬時間が重要になっています。PCBトレースは送信ラインとしても作用するので、信号トレース長が重要になります。1cmのトレースは60~75psの伝播時間に相当します。これと、6GHzサンプルクロックのクロック周期、166psを比較してください。ボードレベルの現象が著しく設計に影響することが分かると思います。これにより、高速サンプリングシステムにおいてはPCBレイアウトが決定的な成功要因である理由が説明できます。しかし、事態を困難なものにする要因がもうひとつあります。それはデジタルドメインに関係するもので、メタスタビリティと呼ばれます。

ESIstreamは、SYNCチェーンによってレイテンシを確実に制御できます

メタスタビリティは、デジタル技術における不確定状態を意味するものです。サンプルレートの増加に伴い、これはシステムタイミングにおける潜在的な問題の主要原因のひとつになるものです。同期化にはメタスタビリティへの対策が必要で、その解がSYNCチェーンです。

簡単に実装できて安定動作させることができるタイミング同期方法は、多くのシステム設計者に歓迎されると思います。Teledyne e2vでは、イベントドリブン型の差動電気信号であるSYNCと同期出力信号(SYNCTRIGおよびSYNCO)によって、確実に同期させる方法を確立しました。これらの信号は、ターゲットとなるコンバータのタイミングシステムをリセットすることも可能で、全てのデジタル・サブシステムをリファレンス・マスタークロックに適切にロックさせることができます。さらには、この同期手法はより大規模なADCシステムに適用することも可能です。

このアプローチの利点はシンプルであることです。追加のクロック信号を必要とせず、システムの長い稼動期間全体に渡って、多チャンネル間で安定的に同期することを保証します。一度設計が完了して生産体制が整えば、ただ一回のトレーニングサイクルを実行するだけで正確なシステム同期を実現できます。温度や電圧などの環境条件の変化があった場合でも、同じシステムタイミングパラメータそのまま使用することができます。SYNCチェーンは、確実なシンクロナイゼーションを実現できます。これは大量生産へ移行する際の大きなメリットになります。

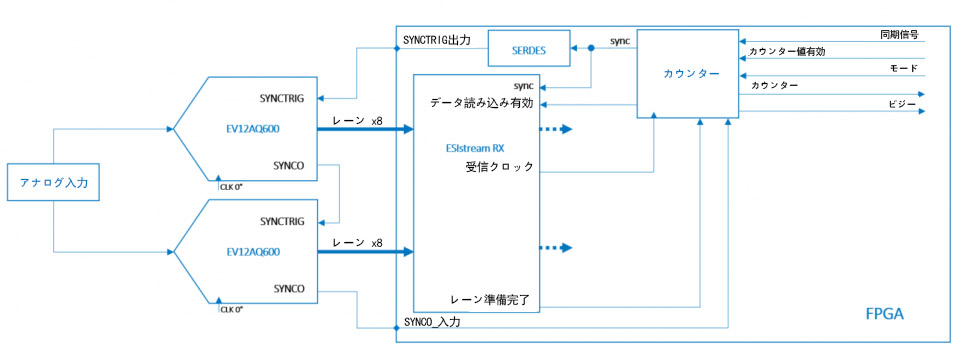

続いて、ESIstreamリンクの受信端上でレイテンシを的確に把握するために、受信エラスティック・バッファーの後段にシンプルなカウンターが実装されています。このカウンターで伝送路の最大レーンレイテンシを個別に補償することができます。

図9 ESIstreamレシーバ内のフレームカウンター

FPGAに実装されるカウンターモジュールは、SYNCTRIGの立ち上がりと「全レーン受信準備完了」イベントの間の受信クロック数をカウントします。この情報は、エラスティック受信バッファリングと連携して全システムの受信データの完全な同期を可能にします。従って、ESIstreamを使用したシステムはSYNCチェーンだけで完全な同期化を図ることができるのです。

ESIstream VHDLモジュール – 開発のゴール

ESIstreamの採用を容易にするために、ESIstreamを開発したTeledyne e2vは2018年後期にXilinxやIntelのFPGAで使用することができるESIstreamのIPブロックの供給プロジェクトを開始しました。IPはさまざまな速度での運用が可能で、宇宙認定レベルでの運用にも適しています。もちろん、IPは当初からTeledyne e2vの製品に適した性能を提供することにフォーカスしています。しかしこの基本機能を有するIPに加えて、広い範囲のサンプルレートをカバーするダイナミックに再構成可能なラインレート・モジュールを開発しているところで、より広範な顧客の要望に応えようとしています。

シリアル化の未来に向けて

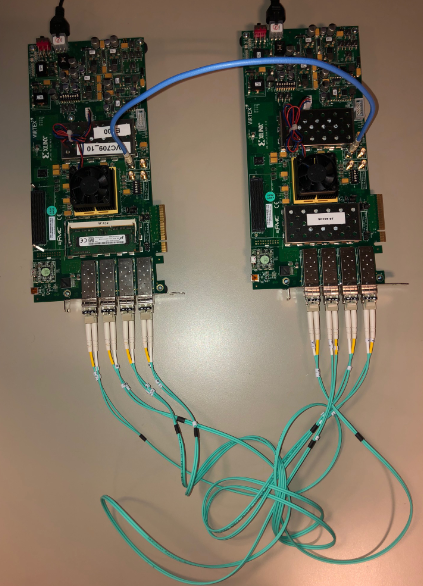

Teledyne e2vは次世代の技術にも目を向けており、ESIstreamの物理層を光ファイバーで伝送する技術を研究しています。光ファイバーを使うと、銅線を使用したインターフェース(PCBトレースや同軸ケーブル)を使うに比べて、コンバータをFPGAからかなり離れた位置に置くことができます。このことは、それぞれ6 Gspsで作動する4本のSFP(低フォームファクターでプラグ着脱可能)を使用した光ファイバーを通じて接続された、2基のXilnx VC709評価ボードを使用して実証しています。

図10 光ファイバーを使用したESIstream物理層の伝送実証

VHDLコードモジュールは、Teledyne e2vの社内検証を完了したら、当社ウェブサイトから無料でダウンロードして利用できるようになるでしょう。

ESIstreamのJEDECとの比較

ESIstreamのシステムレベルでのメリットは、以下のものが挙げられます。

- 各デバイスのLMFCクロックが不要になので、LMFCクロックの取り扱いに苦労することがありません。

- 単一デバイスで使用される場合、複数デバイスをSYNCチェーン接続で使用する場合、共にPCBのESIstream SYNC信号の配線長を気にする必要がありません。

- ESIstreamは、SYSREF信号が必要がないため、JESD204Bサブクラス1と比較してハードウェアの複雑性が軽減されます。

- ESIstreamのSYNC信号は、前に述べたSYNCトレーニングと呼ばれる機能で使用されます。ESIstreamでは、たった一度ののトレーニングを行うだけです。いったんレイテンシ・パラメータが求められれば、それは固定されたものとなります。つまり、ESIstreamは、生産へとスケールアップできる、より簡単なインターフェースなのです。

| JESD204B | ESIstream |

| 工業標準 | オープンソース |

| 市販IP() | VHDLコードモジュール |

| オーバーヘッドと電力が変動 | 低リソース & 低オーバーヘッド |

| レイテンシの把握が困難 | レイテンシを正確に把握できる |

| 同期状態の検出 | |

| 低いリンクレイテンシ | |

| IPライセンスフィー不要 | |

| 低電力 |

結論

JESD204Bサブクラス1および2に記述されたJEDECデータシリアル化アプローチは、マルチチャンネル・データコンバータ・システムを完全に制御するための課題を解決したように思われます。これは一部では真実ではあるものの見逃されがちなのは、複雑なトランスポート層、物理層の要求仕様を取り扱う場合に設計者が直面する多くの課題があることです。

エンジニアは、JESD204BライセンスやコアIPを購入して信号プロセッシングSoC(FPGAあるいはASIC)に組み込むだけで、システム設計課題のほとんどが解消されると期待するかもしれません。しかし報告された実情によれば、JESD204Bのマルチドメイン・クロックの複雑性によって、課せられたタイミングの制約を全て満たすPCB設計を行うためには膨大な開発リソースを必要することが実証されています。

これには優れた解決策があります。それはESIstreamです。ESIstreamはオープンソースで、誰もが無償で使用できます。ESIstreamは性能面でJESD204Bに匹敵しますが、より優れたユーザー体験をもたらします。よりシンプルで設計が簡単で、電力を削減できます。信頼できるIPブロックとVHDLコードモジュールが御利用可能ですので、採用を阻むものはありません。Teledyne e2vが今後提供する新しいデータコンバータに対応したIPブロックも、現在開発しております。さらに、御客様は御客様独自の高速シリアルプロジェクトのために、VHDLコードモジュールを無料でダウンロードできます。

編集者への注記:

Teledyne e2vについて

Teledyne e2vはその技術革新により、ヘルスケア、ライフサイエンス、宇宙、輸送、軍事安全保障、工業といった市場の発展を牽引しています。Teledyne e2vはそのユニークなアプローチにより、市場とお客様の課題を丹念に吸い上げ、お客様と協力しながら革新的なソリューションを提供していきます。ソリューションは、標準的なものだけでなくセミオーダーや完全にカスタマイズされたものにも対応し、お客様のシステムの価値を上げます。Teledyne e2vは、リエンジニアリング/アップスクリーニング技術における世界的なトップ企業です。30年以上にわたるNXPとの戦略的パートナーシップをもち、NXPの商用プロセッサーの宇宙、ミリタリ、インダストリアル・グレード製品を生み出してきました。Teledyne e2vは、NXPの試験ベクトルを使用し、QorIQ® Power® アーキテクチャー、NXPのLayerscapeシリーズに信頼性という付加価値を持たせています。

詳細はこちらをご覧ください。FPGA

ESIstream IP製品について、詳しくは当社までお問い合わせください。

お問い合わせ

すぐにビジネスを支援するには、以下の情報を入力してください