## 2021年4月

### 抄録

ADC や DAC の性能仕様やフォームファクター、そして新たなセンサー技術(Rx、Tx)の進化とともに、RF データ変換システムも急速に変化しています。システムレベルの設計上の課題として共通しているのはオフログ回路とデジタルの実装上のアおよっているのはオフテルの自由では、システークの根でで、の根ででは、システムとは、システムとは、システムとはにはにないででは、システムには、システムにはにはにないででは、システムがあります。現在では、システムがあります。現在を活度な SiP (システムインパッケージ) 組み立て技術を

用することで、データ変換システム設計の実装がハードウェア中心からソフトウェア中心へと変わります。Teledyne e2vでは、SiP 設計、開発、組み立てのノウハウを活かし、最大限の柔軟性確保とでの設計に向けてシステムレベルでの設けでは、ないでは、での対応に向けてシステムレベルでの設けがある。RF、ミックスドシがのといます。RF、ミックでは、ボインリップが、計測、通信、軍事、宇宙アプリケージなど、音楽、航空、計測、通信、軍事、宇宙アプリックを実現しています。Teledyne e2vには、40年以上にわたる高度な SiP 設計および組みステムの場所することでで、140年級がの最高の性能と価値を発揮する高度なデータ変換がて最高の性能と価値を発揮する高度なデータ変換システムのプラットフォームを実現します。

### SIP 設計のための高度なデータ変換コンポーネント

高周波データ変換システムには、シグナルチェーン全体の重要な機能に対応する高性能で信頼性の高い半導体デバイスが必要です。SiP 実装には、システム全体の性能要件を満たす適切な半導体を選択することが不可欠です。Teledyne e2v では、高速データコンバータ、マイクロプロセッサ、メモリ、そしてさまざまなアナログおよびロジック機能を SiP 実装用に提供しています。

もちろん、データ変換受信(Rx)システムの中核をな すのは ADC です。Teledyne e2v は、20 年以上にわた ってデータコンバータ技術に革新をもたらしてきまし た。そして、(上の写真にある EV12AQ600 のような) マイクロ波の周波数域で動作するマルチチャンネルで ノイズや歪みの低い ADC を提供しています。このタイ プのデータコンバータでは、周波数のダウンコンバー ジョンのために従来のアーキテクチャで必要だったア ナログ段を、(ダイレクト RF コンバージョンによって) システム設計者は排除することができます。また、当 社のハイエンド ADC ではアナログ段を削減し、高度な SiP 設計技術を標準ソリューションおよびカスタムソ リューションとしてライセンスフリーで利用できます。 これにより、標準製品およびカスタムソリューション を利用しながら、特定の性能品質要件や環境要件を満 たす設計を実現できます。

今後、高速 SiP ダイレクト RF データ変換受信(Rx) ソリューションの中核を担うのは、EV12AQ600 です。 実験用 SiP である RF フロントエンドレシーバ基板(下 図)、PS620は、RTH120トラックアンドホールド増幅 器(THA)と組み合わせることで、最高水準の性能を 達成しました(使用デバイスの主なパラメータは2ペ ージを参照)。 EV12AQ600 はクアッドコア ADC で、ク ロスポイントスイッチ(CPS)フロントエンドを搭載 しており、ADCの4つのコアを同時に、独立して、あ るいはペアで動作させることが可能です。これにより、 クワッドチャネルでは 1.6 GSps、デュアルチャネルで は 3.2 GSps、シングルチャネルでは 6.4 GSps で動作 します。(第2高調波(H2)と第3高調波(H3)なし の) クワッドチャネルモードでの 5980 MHz までの SFDR は、-1 dBFS で 70 dBFS 以上を達成していま す。

## 2021年4月

EV12AQ600 は、民間商業市場から産業、軍事用まで、さまざまなグレードに対応します。さらに放射線耐性の必要な宇宙レベルの品質にも対応します。EV12AQ600 は、高速データ収集や高速試験計測だけでなく、自動試験装置、地球観測 SAR 衛星ペイロード、通信 MIMO 衛星ペイロード、超広帯域衛星デジタル受信機、C バンドダイレクト RF ダウンコンバージョン、マイクロ波ソフトウェア無線、ポイント・ツー・ポイント・マイクロ波受信機、機械状態監視システム、TOF型質量分析計、LiDAR(光検出と測距)、高エネルギー物理学など、様々なアプリケーションに適しています。

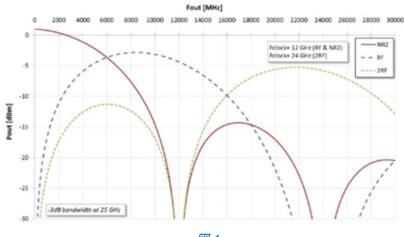

最先端の高速 SiP データ変換送信 (Tx) ソリューションを実現する上で重要な技術は、EV12DD700 (右図) です。このデュアルチャンネル 12 ビット DAC は、最大 12 GSps の動作が可能であり、ダイレクトRF 出力信号発生は 21 GHz まで、フルスケールのステップ応

答時間は 15 ps を達成していて、マイクロ波周波数の市 場において最もノイズが少なく最高の性能を実現して います。EV12DD700 はデュアルチャンネル DAC で、 Ka バンドまでの周波数にも対応しており、ビーム形成 アプリケーションをサポートします。この DAC の出力 帯域幅は、25 GHz までは 3 dB、25 GHz を超える領域 でも3 dB をわずかに上回る減衰量です(図1参照)。 各 DAC とも一連の高度な信号処理機能を備えており、 プログラム可能な逆 sinc フィルタによるダイレクトデ ジタルシンセシス (DDS) 機能やプログラム可能な複 素ミキサ、さらにデジタルアップコンバータと 4 つの 補間ステージも搭載しています。デジタル処理機能と しては、補間(比率 4X、8X、16X)、数値制御発振器 (32 ビット NCO) によるデジタルアップコンバージョ ン(DUC)、ダイレクトデジタルシンセシス(DDS)、 デジタルビーム形成、ビームホッピングがあります。 DAC の主な特徴としては、プログラム可能な出力モー ド(NRZ、RF、2RF)、ゲイン調整、プログラム可能な SINC 補償機能、およびマルチデバイス同期があります。

#### 使用デバイスの主なパラメータ

#### EV12AQ600 ADC

- 4 つの 12 ビット 1.6 GSps ADC コアにより、1、2、4 チャネルのタイムインターリーブをサポート

- 完全インターベールドモードによる 6.4 GSps までのサンプリング

- · 6.5 GHz の入力帯域幅(-3dB)

- ・ 統合された広帯域クロスポイントスイッチ

- · マルチチャンネルの同期を実現する Sync チェーン

### RTH120THA:

- · 24 GHz の入力帯域幅

- デュアル THA によるサンプルクロックの半分以上 の出力ホールドタイムを実現

- · 完全差動型設計

#### 3 種類の出力モードにおける DAC 出力特性

### 2021年4月

当然のことながら、高速データ変換システムには高度なデジタル処理能力が必要です。その例が、Teledyne e2vのリリースした LS1046A です。このマイクロプロセッサは、NXPの新たな Layerscape®シリーズからアップスクリーンして認定した製品で、-55℃~125℃で動作します(LS1046-Space も近日中にリリース予定)。LS1046A は NXP の 64 ビット Arm® Layerscape ポートフォリオの 1 つで、クアッドコア Arm® Cortex® A72設計を採用しています。

この設計により、Arm®テクノロジーと互換性のあるソフトウェアサービス、アプリケーション、ツールの広大なエコシステムを、最高の性能かつ最もコンパクト

なフォームファクターで利用することができます。 LS1046A は 1.8 GHz で動作するプロセッサで、パケッ ト処理のアクセラレータと高速周辺インタフェースを 統合しており、その高性能なアーキテクチャと市場を リードする処理能力に定評があります。45,000 CoreMarks®以上の演算性能(1.8 GHz で 30K DMIPS) と、デュアル 10 Gb イーサネット、3 つの PCle Gen3、 1 つの SATA Gen3 とを組み合わせることで、高い信頼 性が要求される軍事航空(および宇宙)アプリケーシ ョンに最適です。LS1046A は、Teledyne e2v の最新の Qormino®計算モジュールにも採用されており、4 GB の DDR4 メモリも搭載されています(左の写真参照)。 さらに、Teledyne e2v の半導体ライフサイクルマネー ジメントプログラム SLiM™の一環として、このデバイ スの寿命は15年以上にわたりサポートされ、コストが かかりがちな生産中止や保証対象外という問題を回避 できます。

### すべての市場で必要となるデータコンバージョン SiP を実装したシステムのピーク性能

データ変換システムは、産業、医療、航空、計測、通信、軍事、宇宙など様々な分野で使用され、急速に少れています。どの市場区分にも共通するシステムレベルにおける設計上の課題は、アナログロスをとりコンスをとり、フトウェアやシステムの柔軟性(センサーからとして、または高めることです。この根では、システム設計において、デーションを展大限活用する必要があります。

システム設計エンジニアは、市場やアプリケーション、ハードウェアの仕様等の要件を理解していますが、一方で、高性能データ変換システムに関連するリスク、技術の選択、フォームファクター、開発スケジュール (スケジュールの同期化を含む)、信頼性、コストなどの設計パラメータは非常に変わりやすいものです。こ

れらの設計パラメータと、変化し続けるシステム性能の仕様要件とを合わせて考慮すると、最終的に設計実装の「重なり」の部分が絞り込まれてきます(図 2 参照)。もちろん、どのような設計パラメータであっても、ミスがあれば非常に大きな損失につながります。このため、実際にプロジェクトの全体的な価値を高め低下させないのであれば、設計開発段階から自由度を確保することは十分投資に値することなのです。

図2 - 設計パラメータとシステムレベルの性能要件を 高めると、実装の「重なり」の部分が絞り込まれる

## 2021年4月

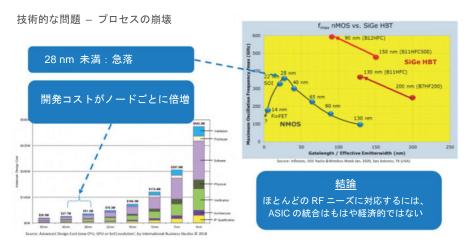

開発段階から自由度を高め最終的に市場で要求される性能要件を満たすことが可能な設計手法の 1 つは、特にデータ変換システムにおいては SiP (システムインパッケージ) 技術を利用した機能を実装することです。これまでシステムレベルの設計者は、進歩し続ける半導体プロセス技術により、SoC (システムオンチップ)

に完全な回路機能を実装してきました。特に負荷の高いデジタル演算が必要な SoC アプリケーションは、ゲート長が 10 nm 以下の半導体技術を用いて実現されてきました。しかし残念ながら、半導体がコンパクトになるにつれ、チップ開発コストは指数関数的に増加します(図 3 参照)。

**3**

図 3 は、最小ジオメトリのゲート長とデバイスの最大発振周波数との相関も示しています。この図からは、Fmax がゲート長 28 nm 未満で急落していることがわかります。それとともに、開発コストはゲート長が短くなるにつれて指数関数的に増加します(平均開発コストは、例えばゲート長 28 nm では 5130 万ドル、ゲート長 16 nm では 1 億 630 万ドル、ゲート長 7 nm では 2 億 9700 万ドル、ゲート長 5 nm では 5 億ドルを超える)。

このため、オンチップ機能が増加するにつれゲート長

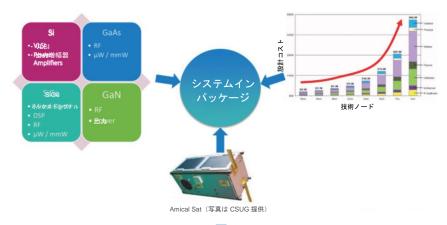

を短くする必要があり、SoC 開発コストは膨大になります。例えば携帯電話業界では SoC が主流でしたが、MEMS センサーなどのアナログ技術への要求が高まるにつれ、SoC から SiP 実装へ移行する傾向が生まれています。図 4 では、現在 SoC から SiP 実装への移行を促している 3 つの共存設計パラメータを示しています。その 3 つとは、1)技術:最適なシステム性能を実現するための適切なプロセス技術の選択(Si、GaAs、GaN、SiGe など)、2)微細化、3)コストです。

## 2021年4月

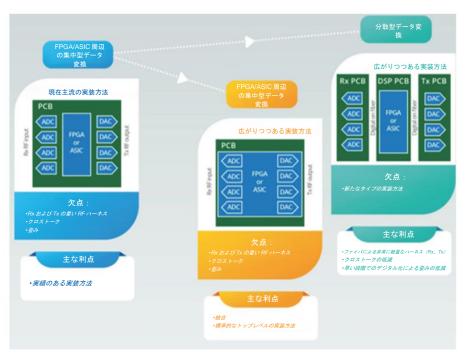

データ変換システムの開発が SoC から SiP 実装に移行している要因は、もう 1 つあります。その要因とは、データ変換回路コンポーネントを区画化(または連結)することが必要になったからで、アナログおよびデジタル信号をルーティングし、複数の実装方法が可能になるようにソフトウェアリゼーションを最大限活用する必要があります。簡単に言えば、データ変換システムは、「集中型」または「分散型」システムとして設計

することができるのです(図 5 参照)。集中型データ変換システムでは、アナログ信号のルーティングが必要なため、クロストークや歪みの影響を受けやすくなります。これに対し分散型データ変換システムでは、ADCをRxセンサーに、DACをTxセンサーに配置できることから、デジタル信号を基板上で、軽量でコンパクトな高速データレートのファイバ接続によってルーティングすることが可能です。

**Ø** 5

その結果、Teledyne e2vの高度な SiP 設計、開発、組み立てのノウハウは、データ変換システムの開発に革新をもたらし、マルチミッション機能のための設計パラメータの自由度(連結や区画化など)を最大限に高めてきました。RF、ミックスドシグナル、デジタル処理半導体をワイヤボンディング、フリップチップなどの最新技術を活用して連結(または区画化)することで、高度な SiP 設計および組み立て技術により、高周波データ変換システムのプラットフォーム設計が低コストで実現でき、かつ最高のパフォーマンスをもたらします。

**⊠** 6a

## 2021年4月

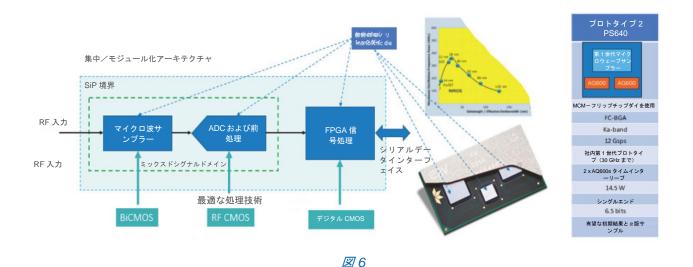

例えば、図 6 に示す PS640 は現在開発中の SiP 実装の RF データ変換システムで、将来的には L から Ka バンドまでの高周波レシーバ(1  $GHz\sim40~GHz$ )として使用できます。

PS640 は Teledyne e2v の設計した新たな THA を STMicro BiCMOS055 プロセスで利用し、2 つのインタ リーブされた EV12AAQ600 ADC を「集中型」高速 SiP データ変換レシーバ(Rx)として実装しています。図

6には、性能仕様の測定値も示しています。図7は、同じデータ変換システムが、将来的に「分散型」データ変換レシーバとして実装された場合の概念を示しています。デジタルプロセッサ(FPGA)を駆動する(SiPに搭載された)光学エンジンを利用して、最大のソフトウェアリゼーション(ソフトウェア中心とすること)を実現します。

分散型アーキテクチャ

SiP 境界

SiP 境界

OE + FPGA OE + OE OE + OE + OE OE + OE + OE OE OE + OE OE + OE OE + OE OE OE + OE

図7

# 2021年4月

### Teledyne e2v の高度な SiP 組み立て技術

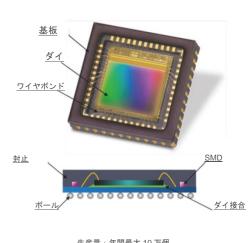

SiP は複数の素子(受動および能動)を連結して1つのパッケージにまとめた単一のデバイスで、電子システムレベルでさまざまな機能を実現します。SiP に組み込まれる半導体デバイス(受動素子を含む)は、基板上に水平または垂直に実装された後、パッケージ化されます。半導体と基板素材とは、ワイヤボンディングまたははんだバンプ(この場合はダイスを垂直に積むことも可能)で接続します。

前述のように、データ変換 SiP には、プリアンプ、ミキサ、ADC、DAC、専用のプロセッサ、メモリ集積回路に加え、抵抗器やコンデンサなどの受動素子も含まれています。これらはすべて同じ基板上に、さまばな方法で取り付けられています。SiP 組み立て技術はあらゆる市場に進歩をもたらし、特に超高周波(地上のインターネット)、モバイルおよびウェアラブルデバイスなどのアプリケーションで活用されています。SiP 技術を利用した製品とパッケージソリューションには充まざまなものがあり、Teledyne e2v は産業、医療、空宇宙、軍事、科学、宇宙アプリケーションなどの分

野で設計および組立サービスを提供しています。また、Teledyne e2v の製品の多くは、NXP、Everspin、Micronといった企業との戦略的パートナーシップを通じて開発されています。

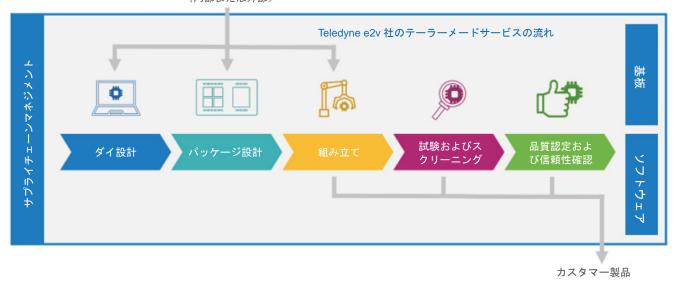

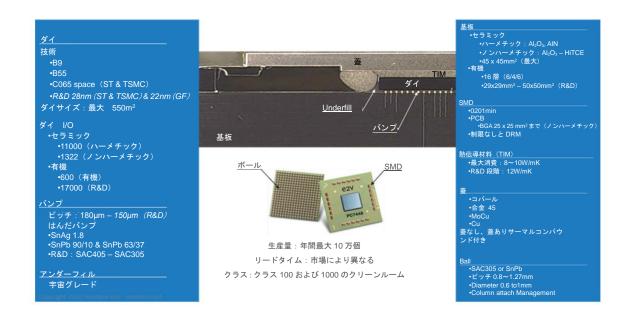

Teledyne e2v では SiP 設計開発用のサプライチェー ン・マネジメントサービスを幅広く提供しており、そ のラインナップには、ダイ設計、パッケージ設計、高 信頼性組み立て技術、高性能の実測度テスト、品質認 定サービス、SLiM™ブランドの半導体ライフサイクルマ ネージメントなどがあります(図 8 参照)。Teledvne e2v には 40 年以上にわたる宇宙向け ADC、DAC、マイク ロプロセッサ、メモリの設計と、社内試験および認定 サービスの経験があります。その経験によって、あら ゆる認定レベルの要件に対応した高度な SiP 製品およ びサービスをあらゆる市場に提供することができます。 Teledyne e2v の高度な SiP 組み立て技術には、ワイヤ ボンディング、フリップチップ、有機およびセラミッ クパッケージ (ハーメチックおよびノンハーメチック) などがあり、さらに多様なデバイスを統合して組み立 てることも可能です。

お客様の要求 (内部または外部)

**図**8

## 2021年4月

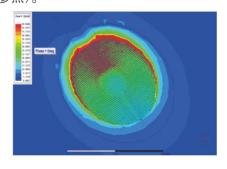

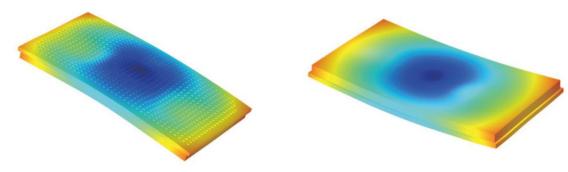

もちろん、高度な高速 SiP の開発では、組み立て前に パッケージ特性を測定するとともに、シミュレーショ ンによって熱と信頼性の双方を検討する必要もありま す。前述の PS640 の熱シミュレーションの例を図 9 に

図 9 - PS640 SiP の伝熱シミュレーション

示します。複数のダイを近接して配置することは、熱設計の面で難しい課題です。コンポーネントの最もクリティカルな接合部の温度予測には、できる限り詳細な熱伝導シミュレーションが必要です。Teledyne e2vでは境界条件を利用し、システム設計者やお客様ともに検討しながら、最終的に測定値と適合するような性能のシミュレーションを目指します(SiPの実装により組み込むコンポーネントに必要)。また、RF SiP 開発のシミュレーションと設計において、高周波 3D フィンドソルバ(Ansys HFSS)も活用しています。HFSSは市販の有限要素法による電磁的構造のソルバで、SiPパッケージに含まれる複雑な RF 電子回路や半導体をパッケージに含まれる複雑などのパッケージと設計に使用でいます(右図 10 参照)。この例では、Teledyne e2vの SiP プロセス開発のフローに沿って、パッケージチ

ームと半導体設計チームが協力し RF アナログフロントエンドを共同設計しました。

SiP の信頼性を確保した設計はエンジニアリング上の大きな課題です。1 枚の有機基板にはさまざまなシリコン技術が搭載されており、C4 (controlled collapse chip connection: はんだバンプを使用したフリップチップによる接合) および C5 (はんだボール) の電気機械的インターフェースに RoHS 適合のはんだ接合が形成されています。Teledyne e2v では高度な技術の開発を続けており、はんだクリープや粘塑性などの非線形挙動を考慮した熱機械解析により、歪みの迅速かつ正確な予測や基板レベルでの信頼性の確保を目指しています(図 11 参照)。

図 10 - 3D フィールドソルバ (Ansys HFSS) を使用したシミュレーションの抜粋。PS640 に 40 GHz のアナログ入力をした場合の THA のパッケージとシリコンダイ間の移行を示しており、シリコンメタルフィリング中の信号伝搬が解析されています。

図 11 - 室温で組み立てた後の PS640 パッケージの歪みを 50 倍に拡大した図

## 2021年4月

専門的な設計および組み立てサービスでは、カスタム 製品、少量から中程度の量、高信頼性/ハイエンド、 QML-V および QML-Y 認証、宇宙グレード認定などに 対応します(下図 12 の技術概要も参照)。

#### ウェハバックエンド

- 全自動: ソーイングおよび UV 照射

- 先進的な洗浄液

- 目視検査

#### /H H I. -

- 非常に長いダイ

- ガラス蓋による封止

- ・光学シールド位置決め

- ・ 光学フィルタ組み立て品

- 自動化されたライン

#### 試験および測定

- ウェハプローブ6インチおよび8インチ、 パッケージ試験: Teledyne IP750

- ・CCD および CMOS

- ・ 完全な電気光学特性評価のための専用ベンチ

- 幾何学的測定

#### 表面実装デバイス

- 自動プリント装置、3D スクリーン 技術

- 全自動チップシューターによる表面実装

- シングルパッケージおよびパネル工程

- 雰囲気制御マルチゾーンオーブン

#### スクリーニングおよび品質認定

- バーンイン、温度サイクリング、サーマルショック

- 移動体粒子検出および目視検査

- 密封試験

- ・ロット検証試験

- 宇宙グレード・軍事グレード品質認定

#### ライフサイクルマネージメント

- 安全な専用保管場所

- 長期間にわたる供給方式

- ・ウェハ保管から始まる 20 年以上の 供給実績

図 12 - SiP 組み立てに利用される Teledyne e2v の高度な組み立て技術

生産量:年間最大 10 万個 リードタイム:市場により異なる クラス: クラス 100 および 1000 のクリーンルーム

### 2021年4月

図 13 - Teledyne e2v のワイヤボンド(上)およびフリップチップ(下)による高度な組み立て技術、SiP 組み立てに利用可能

図 13 に、Teledyne e2v の先進的な SiP ワイヤボンディングおよびフリップチップ組み立て技術を示します。 ワイヤボンディングに関しては、図 13 (上) に示すように、必要な半導体のタイプ (Si、GaN、GaAs など) やパッケージタイプに合わせた最先端の組立には、 まざまなバリエーションの技術が必要となります。 まざまなバリエーションの技術が必要となります。 新たな世代の半導体やパッケージがリリースされる技術の開発が必要になります。 ワイヤボンディングは、 アージ組み立ての約3分の2を占めています。 シリーネントのように、 高度なフリップ接続ができなります。 このような場合でも、コストや信頼性の面でワイヤボンディングが有利です。

フリップチップ技術(前述の図 13)では、半導体の上にバンプアレイや銅ピラーを形成します。フリップチップの製造は従来のIC製造と似ており、IC製造の工程にいくつかの工程を追加したに過ぎません。製造工程の最終段階の前には、接合用パッドに金属をつけるなどの準備をして、はんだが付着しやすくするように加

工します。その後、ウェハプロセスの最後に、はんだ バンプをウェハ上面のチップパッドに配置し、通常の 工程どおりにチップをウェハから切り出します。この チップを外部回路(SiP回路基板や他のチップ、ウェハ など)に実装するため、チップを裏返して上面を下に 向け、パッドが外部回路の対応するパッドと向き合う ように位置合わせをして、はんだをリフローして接合 を完了します(通常は、超音波熱圧着または代替のリ フローはんだプロセスを使用)。またこのプロセスでは、 チップ回路とその下のマウントとの間にわずかな空間 が残るため、多くの場合、電気的に絶縁する接着剤を 「アンダーフィル」することで機械的接合強度を高め、 ヒートブリッジを形成してチップやシステムのはんだ 接合部に熱勾配による応力がかからないようにします。 アンダーフィルにより、チップと基板の間にある熱膨 張の不整合を分散させ、早期故障の原因となるはんだ 接合部への応力集中を回避します。フリップチップ技 術は、ワイヤボンディングとは異なり、チップを上向 きにして、チップパッドと外部回路をワイヤーで接続 する技術です。

### 2021年4月

### Teledyne e2v: ワンストップショップとして、高度な SiP 設計および組み立て技術サービスを 提供

SiP では、他の設計オプション(SoC など)と比較して、特定の製品やシステムの性能寿命にかかるコストを全体的に削減できます。SiP には、以下のように、製品ライフサイクルのあらゆる段階で、システム開発コスト全体を削減できるメリットがあります。

- 1. エンジニアリングコスト削減:技術開発にかかる時間や材料を節約でき、また市場投入までの時間を短縮できることから、設計完了までの労力を大幅に低減できます。

- 2. プリント基板回路コスト削減:(COTS またはカスタム半導体を利用することで)特定のコンポーネントの開発や利用を簡素化できます。

- 3. 組み立てコスト削減:複数のコンポーネントを単 ーのパッケージに統合することで、システム製造 の全工程におけるコストを大幅に低減できます。

- 4. サプライチェーンコスト削減:サプライチェーンを簡素化できます。異なるメーカーから調達していた複数のコンポーネントを単一の SiP 実装に置き換えられます。管理するコンポーネントとサプライヤーが減ることで、サプライチェーンを劇的に簡素化できます。

- 5. 検証:サブシステムおよびシステムレベルでの試験と品質認定を行います。

Teledyne e2v の先進的な SiP 設計と組み立てサービスは、すべての市場区分や製品種別にとっての「ワンストップショップ」となります(図 14 参照)。つまり、Teledyne e2v は宇宙グレードアプリケーションの設計、組み立て、品質認定サービスを提供しているため、他のすべての市場分野、アプリケーション、および品質レベルにも対応できるということです。

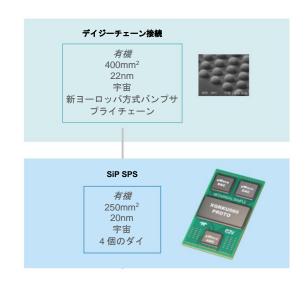

図 14

SiP 技術を利用した先進的なシステム開発が新たな 10 年を迎えようとしている今、ゲート長の微細化が進むことで、半導体の面積が拡大するデバイスを組み立てることが非常に重要になっています。ますます大型化する SoC は、SiP に含まれる多数のコンポーネントの1 つになりつつあります。そうなると、有機基板やパッケージ材料を利用して信頼性のある組み立て(ワイヤボンディングまたはフリップチップ)を行うには、大規模な技術投資が必要になります。現在、Teledyne e2vは今後数年間に見込まれるこれらの技術進歩(右図参照)に対応すべく準備を進めており、この技術開発がすべて ESA によって支援されています。

### 2021年4月

### 結論

現在、データ変換システムの設計者は、半導体プロセスの選択(および幾何学的配列)や回路の小型化への要求、さらに増加の一途をたどる開発コストなど、重大な設計パラメータの課題に直面しています。さらに、新たな ADC、DAC、マイクロプロセッサ、メモリコで制力になる上が続々と登場に重なシステム開発で、前のまでは、まからとで、ではいます。それは、アナログ回路とデジをといるにないます。それは、アナログ回路とデジをといるにないます。それは、アナログ回路とデジをといる。現話の実装上のトウェアやシステムの自由度(センサーからのよび)とです。現在、高度な SiP (システムインパッケージ)組み立て技術を活用することで、全ての市場区分やア

プリケーションにおいて、データ変換システム設計の 実装はハードウェア中心からソフトウェア中心、開発、 組み立てのノウハウを活かし、最大限の柔軟性の確と とマルチミッションへの対応に向けて、システムレールの設計に革命もたらします。Teledyne e2vには 40年以上にわたるパッケージ設計の経験があります。RF、ミックスドシグナルとデジタル処理アプリケーションにおいて、最先端技術(ワイヤボンディング、フリットを表別である。 Teledyne e2vの先進的な SiP 設計と組み立て大力によびダイレクト RF データ変換システムと言語となる。 高周波およびダイレクト RF データ変換システムと言語と記述を提供します。

お問い合わせはこちら:

Yuki Chan,

マーケティング&コミュニケーション

マネージャー

Yuki.chan@teledyne.com

お問い合わせはこちら:

Marc Stackler,

アプリケーションエンジニア

シグナルプロセシングソリューション

Marc.stackler@teledyne.com